如果您希望可以时常见面,欢迎标星收藏哦~

目前市场上有几十种 NPU 选项。每种选项在效率、可编程性和灵活性方面都有相互竞争和冲突的说法。这些选项之间最明显的差异之一是看似简单的问题:在 NPU 系统层次结构中,相对于计算,内存放置的“最佳”选择是什么。

一些 NPU 架构风格严重依赖对系统 DRAM 的直接或独占访问,依赖于大批量商用 DRAM 相对于其他内存选择的相对每比特成本优势,但受制于跨多个芯片的分区问题。其他 NPU 选择严重或完全依赖片上 SRAM 以实现速度和简单性,但硅片面积成本高且缺乏灵活性。还有一些采用新型内存类型 或新型模拟电路结构,这两种类型都缺乏经过验证的、广泛使用的制造记录。尽管 NPU 选择种类繁多,但它们通常与三种内存局部性风格之一保持一致。这三种风格与儿童故事《三只熊》有着惊人的相似之处(双关语)!

儿童童话《金发姑娘和三只熊》描述了 Goldi 的冒险经历,她试图在床上用品、椅子和粥碗的三个选择中做出选择。一顿饭“太热”,另一顿“太冷”,最后一顿“刚刚好”。如果 Goldi 面临在现代边缘/设备 SoC 中为 AI 处理做出架构选择,那么她还将面临三个选择,即计算能力相对于用于存储激活和权重的本地内存的放置。

在、在还是接近?

内存计算 和近内存计算 (CNM:compute-near-memory ) 这两个术语起源于数据中心系统设计中的架构讨论。有大量文献讨论了各种架构的优点。所有分析都归结为试图最大限度地减少在数据中心的处理元件和存储元件之间移动工作数据集时消耗的电量和产生的延迟。

在专门为边缘设备优化的 AI 推理片上系统 领域中,同样的原则也适用,但需要考虑三个接近程度:内存计算、内存计算和近内存计算。让我们快速检查一下每个级别。

内存计算:海市蜃楼

内存计算是指十多年来将计算融入 SoC 设计中使用的内存位单元或内存宏的各种尝试。几乎所有这些尝试都在考虑中的 DRAM 或 SRAM的位单元内采用某种模拟计算。理论上,这些方法通过在模拟域和广泛并行的方式执行计算(特别是乘法)来加速计算并降低功耗。虽然这似乎是一个引人注目的想法,但迄今为止都失败了。

失败的原因是多方面的。首先,广泛使用的片上 SRAM 已经完善/优化了近 40 年,片外存储 DRAM 也是如此。与纯粹的起点相比,使用高度优化的方法会导致面积和功率效率低下。事实证明,将这种新方法注入 SoC 公司使用的久经考验的标准单元设计方法中是行不通的。内存计算的另一个主要缺点是,这些模拟方法仅执行 AI 推理所需计算的非常有限的子集 - 即卷积运算核心的矩阵乘法。但是,没有任何内存计算能够构建足够的灵活性来涵盖所有可能的卷积变化和所有可能的 MatMul 配置。内存模拟计算也无法实现 Pytorch 模型世界中的其他 2300 个操作。因此,内存计算解决方案除了需要具备内存模拟增强功能之外,还需要具备成熟的 NPU 计算能力——当以传统方式使用该内存进行伴随数字 NPU 上发生的所有计算时,“增强功能”会对面积和功率造成负担。

最终分析显示,边缘设备 SoC 的内存解决方案“太有限”,对于勇敢的芯片设计师 Goldi 来说毫无用处。

近内存计算:

近距离计算仍然十分遥远

SoC 推理设计方法的另一端是尽量减少片上 SRAM 内存的使用,并尽量提高批量生产的低成本大容量内存的利用率。这一概念侧重于大规模 DRAM 生产的成本优势,并假设在尽量减少 SoC 上 SRAM 和为低成本 DRAM 提供足够带宽的情况下,AI 推理子系统可以降低 SoC 成本,但依靠与外部内存的快速连接(通常是仅供 AI 引擎管理的专用 DDR 接口)来保持高性能。

虽然乍一看,近内存方法可以成功减少用于 AI 的 SoC 芯片面积,从而略微降低系统成本,但它有两个主要缺陷,会削弱系统性能。首先,这种系统的功耗不正常。请考虑下表,该表显示了将 32 位数据字移入或移出每个 AI NPU 核心的乘法累加逻辑的相对能量成本:

每次从 SoC 到 DDR 的数据传输消耗的能量是本地相邻于 MAC 单元的传输的 225 到 600 倍。即使距离 MAC 单元相当“远”的片上 SRAM 也比片外传输节能 3 到 8 倍。由于大多数此类 SoC 的功耗受限于消费级设备,主要依赖外部存储器的功率限制使得近内存设计点不切实际。此外,始终依赖外部存储器的延迟意味着,随着更新、更复杂的模型的发展,这些模型可能具有比老式 Resnet 更不规则的数据访问模式,近内存解决方案将因延迟而遭受严重的性能下降。

功率过大和性能过低的双重打击意味着近内存方法对于我们的芯片架构师 Goldi 来说“太热了”。

At-Memory:恰到好处

正如孩子们的金发姑娘寓言总是提供“恰到好处”的替代方案一样,内存计算架构是边缘和设备 SoC 的恰到好处的解决方案。再次参考上表的数据传输能量成本,内存位置的最佳选择显然是紧邻的片上 SRAM。将计算出的中间激活值保存到本地 SRAM 中比将该值推送到片外消耗的电量少 200 倍。但这并不意味着您只想使用片上 SRAM。这样做会为每个实现中可以容纳的模型大小设置硬性上限。

对于 SoC 设计人员来说,最好的选择是既能利用小型本地 SRAM,又能智能地调度这些 SRAM 和 DDR 存储器的片外存储之间的数据移动,以最大限度地降低系统功耗并最大限度地减少数据访问延迟。

半导体精品公众号推荐

专注半导体领域更多原创内容

关注全球半导体产业动向与趋势

今天是《半导体行业观察》为您分享的第3943内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

公众号ID:icbank

喜欢我们的内容就点“在看”分享给小伙伴哦

免责声明:该文章系本站转载,旨在为读者提供更多信息资讯。所涉内容不构成投资、消费建议,仅供读者参考。

向新而行|第21届青

向新而行|第21届青

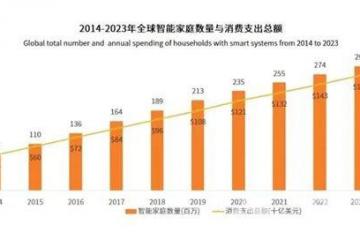

以“高质量”为引擎,智能家居产业怎

以“高质量”为引擎,智能家居产业怎 装智能家居没有零线怎

装智能家居没有零线怎

封阳台的看过来!别人家的大美阳台,

封阳台的看过来!别人家的大美阳台, 原来大多业主都在悄悄

原来大多业主都在悄悄

智能家居为什么从“伪需求”变成了“

智能家居为什么从“伪需求”变成了“ 智慧升级与绿色低碳同

智慧升级与绿色低碳同

Roca推出荣誉一体式智能座厕,升

Roca推出荣誉一体式智能座厕,升